# TC5588P/J-15,-20,-25,-35

# 8,192 WORD × 8 BIT CMOS STATIC RAM

### DESCRIPTION

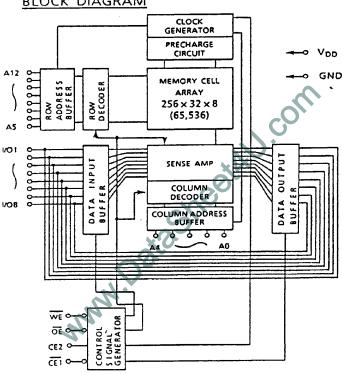

The TC5588P/J is a 65,536 bits high speed static random access memory organized as 8,192 words by 8 bits using CMOS technology, and operated from a single 5-volt supply. Toshiba's CMOS technology and advanced circuit from provides high speed feature.

The TC5588P/J has low power feature with device control using Chip Enable (CEI/CE2), and has Output Enable Input (OE) for fast memory access. Also the device power at memory access is reduced by automatic power down circuit form.

The TC5588P/J is suitable for use in cache memory where high speed is required, and high speed storage. All Inputs and Outputs are directly TTL compatible.

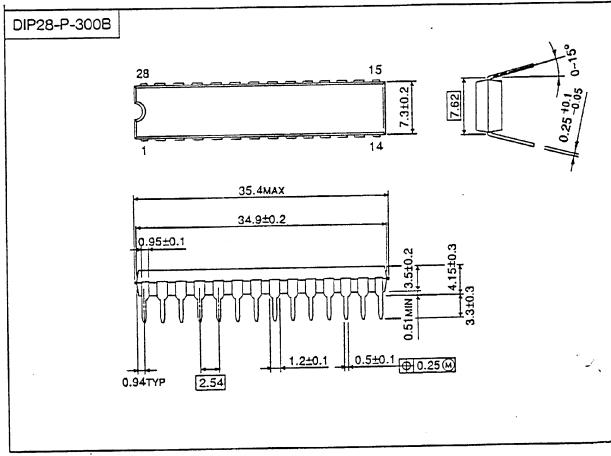

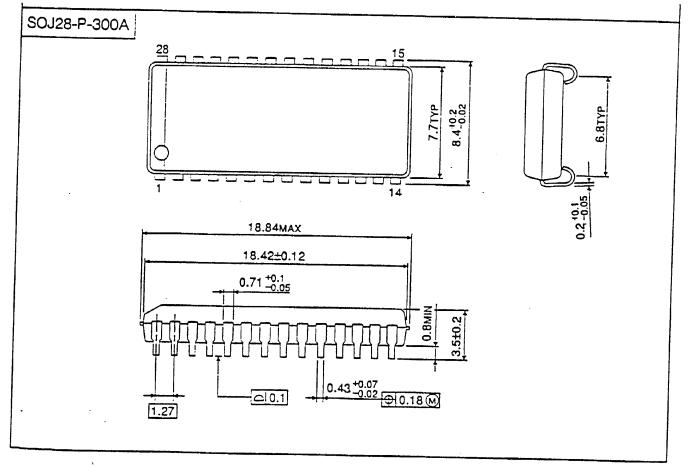

The TC5588P/J is moulded in 28 pin standard DIP and SOJ with 300 mil width for high density surface assembly.

### **FEATURES**

Fast access time:

TC5588P/J-15 15ns (MAX.) TC5588P/J-20 20ns (MAX.) 25ns (MAX.) TC5588P/J-25 TC5588P/J-35 35ns (MAX.)

Low power dissipation:

135mA (MAX.) TC5588P/J-15 Operation TC5588P/J-20 115mA (MAX.)

TC5588P/J-25 115mA (MAX.) TC5588P/J-35 115mA (MAX.)

1mA (MAX.) Standby

5V single power supply: 5V ± 10%

Fully static operation

Directly TTL compatible: All Input and Output

Output buffer control: OE

Package

TC5588P: DIP28-P-300B TC5588J: SOJ28-P-300A

### PIN CONNECTION

| TC5588                                    | P                                                                                                                                                        | TC55                                                                                               | 1881                                                                                                                                                            |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A12 0 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 | 28   VOO<br>27   WE<br>26   CE2<br>25   A8<br>24   A9<br>23   A11<br>22   OE<br>21   A10<br>20   CE1<br>19   I/O8<br>18   I/O7<br>17   I/O6<br>16   I/O5 | N.C. 1 1 1 2 2 A 7 1 3 A 6 1 4 A 5 1 5 A 4 1 6 A 7 A 2 1 8 A 1 1 9 A A 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 28] V <sub>OO</sub><br>27] WE<br>26] CE2<br>25] A8<br>24] A9<br>23] A11<br>22] OE<br>21] A10<br>20] CE1<br>19] VO8<br>18] VO7<br>17] VO6<br>16] I/O5<br>15] VO4 |

| (DIP)                                     |                                                                                                                                                          | (SO                                                                                                | J)                                                                                                                                                              |

### PIN NAMES

| A0~A12    | Address Inputs      |

|-----------|---------------------|

| 1/01~1/08 | Data Inputs/Outputs |

| CET, CE2  | Chip Enable Inputs  |

| WE        | Write Enable Input  |

| ठह        | Output Enable Input |

| Voo       | Power ( + 5V)       |

| GND       | Ground              |

| N.C.      | No Connection       |

### **BLOCK DIAGRAM**

# **AXIMUM RATINGS**

| ANTON IN        | ITEM                         | RATING                    | UNIT     |

|-----------------|------------------------------|---------------------------|----------|

| SYMBOL          |                              | -0.5~7.0                  | V        |

| V <sub>00</sub> | Power Supply Voltage         | - 2.0~7.0                 | V        |

| V <sub>IN</sub> | Input Voltage                | -0.5~V <sub>DD</sub> +0.5 | V        |

| Vout            | Output Voltage               | 1.0                       | w        |

| Po              | Power Dissipation            | 260 - 10                  | °C · sec |

| Tsolder         | Soldering Temperature - Time | - 65~150                  | °C       |

| Tstrg           | Storage Temperature          | -10~85                    | °C       |

| Topr            | Operating Temperature        |                           |          |

# TO RECOMMENDED OPERATING CONDITIONS (Ta = 0~70°C)

| SYMBOL          | PARAMETER                            | MIN.  | TYP. | MAX.                  | ואט |

|-----------------|--------------------------------------|-------|------|-----------------------|-----|

| 31111000        | Power Supply Voltage                 | 4.5   | 5.0  | 5.5                   | V   |

| V <sub>00</sub> |                                      | 2.2   | -    | V <sub>DD</sub> + 0.5 | v   |

| V <sub>IH</sub> | Input High Voltage Input Low Voltage | *-3.0 | -    | 0.8                   | V   |

<sup>\*</sup> Pulse width  $\leq$  10ns, DC: -0.5V (min)

# CC CHARACTERISTICS (Ta = 0~70°C, VDD = 5V ± 10%)

| SYMBOL           | PARAMETER              | TEST CONDITION                                                                                                                           |      | MIN. | TYP. | MAX.         | UNIT     |

|------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--------------|----------|

| 31101000         |                        | V <sub>IN</sub> = 0~V <sub>DD</sub>                                                                                                      |      | -    | -    | ± 1          | μA       |

| In               | Input Leakage Current  |                                                                                                                                          |      | - 4  | _    | -            | mA       |

| он               | Output High Current    | V <sub>OH</sub> = 2.4V                                                                                                                   |      | 8    | _    | _            | mΑ       |

| lou              | Output Low Current     | V <sub>OL</sub> = 0.4V                                                                                                                   |      |      |      | <del> </del> | <u> </u> |

| Ito              | Output Leakage Current | CET = V <sub>IH</sub> or CE2 = V <sub>IL</sub> or WE = V <sub>IL</sub><br>or OE = V <sub>IH</sub> , V <sub>OUT</sub> = 0~V <sub>DD</sub> |      | -    | -    | ±1           | μΑ       |

|                  |                        | V <sub>DO</sub> = 5.5V tcycle = Min cycle                                                                                                | - 15 | -    |      | 135          |          |

|                  |                        | CET = VIL and CE2 = VIH                                                                                                                  | - 20 |      |      |              | m.A      |

| I <sub>D00</sub> | Operating Current      | Other Inputs = VIH/VIL                                                                                                                   | - 25 | _    | ا    | 115          | ""       |

|                  |                        | I <sub>OUT</sub> = 0mA                                                                                                                   | - 35 |      |      |              |          |

|                  |                        | V <sub>DD</sub> = 5.5V tcycle = Min cycle                                                                                                |      |      |      |              |          |

|                  |                        | CET = VIH or CE2 = VIL                                                                                                                   |      | -    | -    | 25           |          |

| loosi            | Standby Current        | Other Inputs = VIH/VIL                                                                                                                   |      |      | ļ    |              | - m      |

|                  | - Standby Current      | $\overline{CE1} = V_{OD} - 0.2V$ or $CE2 = 0.2V$                                                                                         |      |      | _    | 1            |          |

| IDDS2 *          |                        | Other Inputs = $V_{DD} - 0.2V$ or 0.2V                                                                                                   |      | _    | -    | ·            |          |

<sup>\*:</sup> In standby mode with  $\overline{CE1} \ge V_{DD} - 0.2V$ , these specification limits are guaranteed under the condition of  $\overline{CE2} \ge V_{DD} - 0.2V$  or  $CE2 \le 0.2V$ .

# TAPACITANCE (Ta = 25°C, f = 1.0MHz)

| APACITANCE | (1a - 2) C, 1 - 1:0171127 |                        |      |      |

|------------|---------------------------|------------------------|------|------|

| SYMBOL     | PARAMETER                 | TEST CONDITION '       | MAX. | UNIT |

| 3110000    | Laura Canaditanca         | V <sub>IN</sub> = GND  | 5    | pF   |

| CiN        | Input Capacitance         | V <sub>OUT</sub> = GND | 7 .  | pF   |

| Cour       | Output Capacitance        | V001 = 0.10            |      |      |

NOTE: This parameter periodically sampled is not 100% tested.

# AC CHARACTERISTICS (Ta = $0 \sim 70^{\circ}$ C (1), $V_{DD} = 5V \pm 10\%$ )

| EAD CYCL         | E                                   |            | 0041.15        | TC558            | 8P/J-20        | TC558          | 8P/J-25      | TC558          | 8P/J-35        | บทเ  |

|------------------|-------------------------------------|------------|----------------|------------------|----------------|----------------|--------------|----------------|----------------|------|

|                  |                                     |            | 8P/J-15        | MIN.             | MAX.           | MIN.           | MAX.         | MIN.           | MAX.           | UNI  |

| SYMBOL           | PARAMETER                           | MIN.       | MAX.           |                  | <del> </del>   | 25             | _            | 35             | _              |      |

| † <sub>RC</sub>  | Read Cycle Time                     | 15         |                | 20               | <u> </u>       | 23             | 25           |                | 35             | ļ    |

|                  | Address Access Time                 |            | 15             |                  | 20             | <u> </u>       | <del> </del> |                | 35             |      |

| t <sub>ACC</sub> | CET Access Time                     |            | 15             |                  | 20             | <u> </u>       | 25           |                | 35             | 1    |

| tco1             | CE2 Access Time                     |            | 15             |                  | 20             |                | 25           |                |                | ł    |

| tcoz             | OE Access Time                      | -          | 9              |                  | 10             |                | 12           | <u> </u>       | 12             | -    |

| <sup>t</sup> OE  | Output Data Hold Time From Address  | 5          | _              | 5                | _              | 5              | -            | 5              | -              | n:   |

| tон              | Change                              | ļ          | <del> </del>   | 5                | +              | 5              | _            | 5              | _              | ] '" |

| t <sub>COE</sub> | Output Enable Time from CE1 or CE2  | 5          | <del> </del>   |                  |                | <del> </del>   | 6            | _              | 6              | 1    |

| tcop             | Output Disable Time from CE1 or CE2 | <u>  -</u> | 6              | <del>  -</del> - | 6              |                | <u> </u>     | 0              | <del>  _</del> | 1    |

| TOEE             | Output Enable Time from OE          | 0          | <del>  -</del> | 0                | <del>-</del>   | 0              | 5            | <del>  _</del> | 5              | 1    |

| topo             | Output Disable Time from OE         | <u> </u>   | 5              | <u> </u>         | 5              | <del>  -</del> |              | 0              | <del>  _</del> | 1    |

| tpU              | Chip Selection to Power Up Time     | 0          | <del>  -</del> | 0                | <del>  -</del> |                | -            | +              |                | 1    |

| t <sub>PD</sub>  | Chip Deselection to Power Down      | _          | 15             |                  | 20             |                | 25           |                | 35             |      |

| RITE CYC        | LE                          | I TOESR | 8P/J-15      | TC558 | 8P/J-20          | TC558   | BP/J-25        | TC558 | 8P/J-35      | UNIT    |

|-----------------|-----------------------------|---------|--------------|-------|------------------|---------|----------------|-------|--------------|---------|

|                 | PARAMETER                   | MIN.    | MAX.         | MIN.  | MAX.             | MIN.    | MAX.           | MIN.  | MAX.         |         |

| SYMBOL          | 7,44                        |         |              | 20    | -                | 25      | -              | 35    | -            |         |

| twc             | Write Cycle Time            | 15      |              | 13    |                  | 15      |                | 15    | -            |         |

| tcw             | Chip Enable to End of Write | 12      | <del> </del> |       | <del>-</del>     | 0       | <del>  _</del> | 0     | -            |         |

| <sup>t</sup> AS | Address Set Up Time .       |         | <u> </u>     | 0     | <del> </del>     | 15      | <del> </del>   | 15    |              | 1       |

| twp             | Write Pulse Width           | 12      | <del> </del> | 13    |                  | +       | <del> </del>   | 0     | _            | ns      |

| twr             | Write Recovery Time         | 0       | <u> </u>     | 0     | <del>  -</del> - | 0       | <del> </del>   | 12    | <del> </del> | 1       |

|                 | Data Set Up Time            | 9       |              | 10    | <del> </del>     | 12      | ļ- <u>-</u> -  | 0     | <del> </del> | 1       |

| tos             | Data Hold Time              | 0       |              | 0     |                  | 0       | <del> </del>   | +     | +            | 1       |

| t <sub>DH</sub> | Output Enable Time from WE  | 0       |              | 0     |                  | 0       |                | 1 0   | +            | -       |

| toew            | Output Disable Time from WE | _       | 6            |       | 6                | <u></u> | 6              |       | 6            | <u></u> |

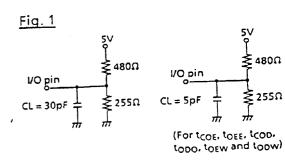

# ACTEST CONDITIONS

| Input Pulse Levels                        | 3.0V/0.0V |

|-------------------------------------------|-----------|

| Input Pulse Rise and Fall Time            | 3ns       |

| Input Timing Measurement Reference Levels | 2.2V/0.8V |

| Output Timing Measurement Reference       | 2.0V/0.8V |

| Levels Output Load                        | Fig. 1    |

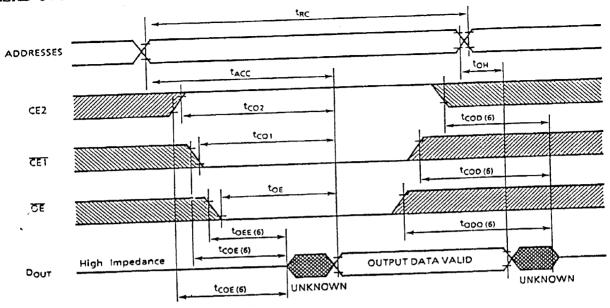

# TIMING WAVEFORMS

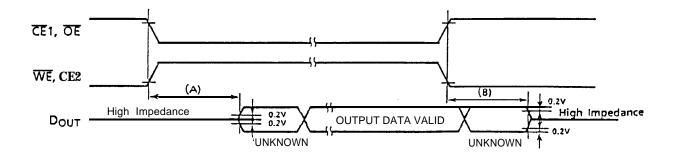

# READ CYCLE (2)

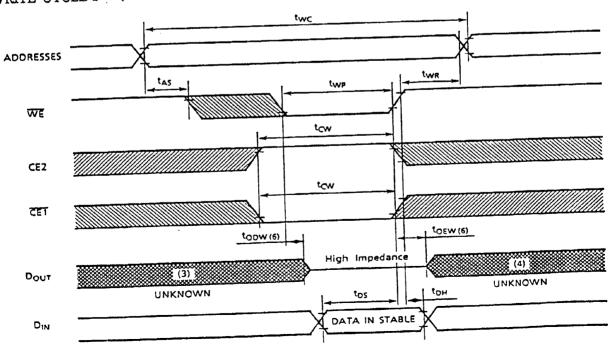

# WRITE CYCLE 1 (5) (WE Controlled Write)

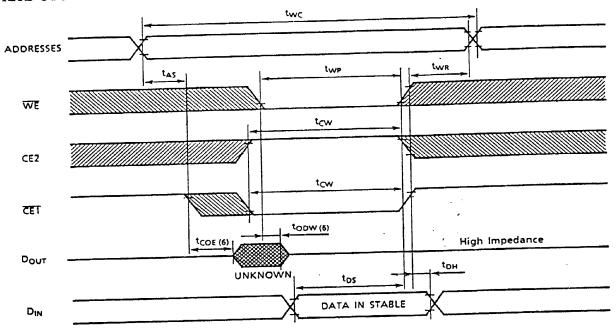

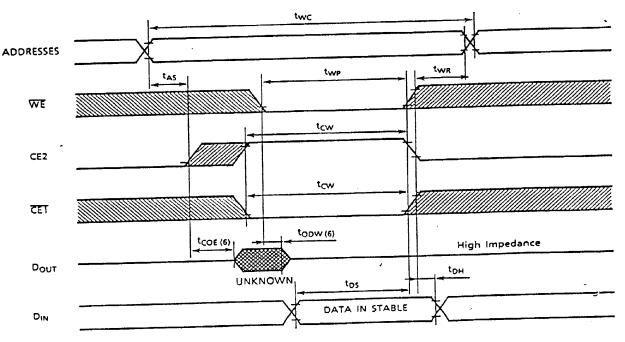

WRITE CYCLE 2 (5) (CEI Controlled Write)

# WRITE CYLCE 3 (5) (CE2 Controlled Write)

- NOTES: 1. The operating temperature (Ta) is guaranteed with transverse air flow exceeding 400 linear feet per minute.

- **2. WE** is High for Read Cycle.

- Assuming that CE1 Low transition or CE2 High t ransi tion occurs coincident with or after WE Low transition, Outputs remain in a high impedance state.

- 4. Assuming that CE1 High transition or CE2 Low transition occurs coincident with or prior to WE High transition, Outputs remain in a high impedance state.

- Assuming that OE is High for Write Cycle, Outputs are in a high impedance state during this period.

- These Parameters are specified as follows and measured by using the Ioad shown in Fig. 1.

- (A) tCOE, tOEE, tOEW ..... Output Enable Time

- (B) tCOD, tODO, tODW ..... Output Disable Time